特點

- 32/40位元IEEE浮點數學

- 32位元固定點乘法器,含64位元乘積與80位元累加

- 無運算管線

- 硬體內有六個零負載迴圈巢狀層

- 豐富的代數組合語言語法

- 指令集支援條件式算術、位元操作、除法和平方根、位元欄位插入和提取

- DMA允許全時脈速率的零負載背景傳輸,不需處理器介入

應用

- 汽車

- 馬達與電源控制

- 製程控制

- 保全與監控

- 測試與測量

影片

特點

- 每個SHARC+核心高達450 MHz

- 每個核心具備高達3 Mb的L1 SRAM記憶體,含同位(選擇性功能,可設定為快取)

- 支援32位元、40位元和64位元浮點數學

- 支援32位元固定數學

- 高效能的DMA系統

- 晶片內建記憶體保護

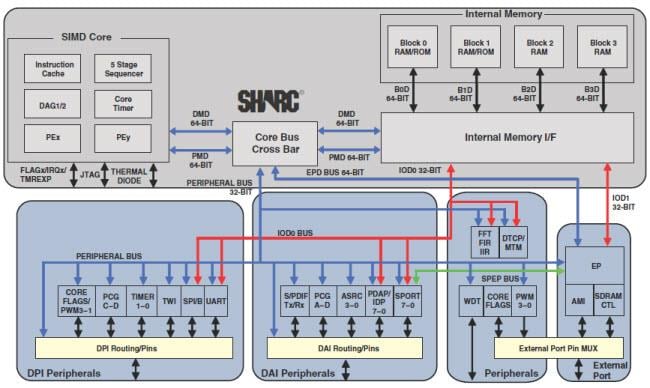

功能方塊圖

Planning For Success In Real-Time Audio Processing

A standalone audio DSP optimized for low latency processing is likely to lead to increased robustness, decreased development time, and optimal scalability to accommodate future system needs and performance tiers.

發佈日期: 2013-05-23

| 更新日期: 2025-10-01